Semiconductor Fabrication Supplier Risks That Delay Capacity Expansion

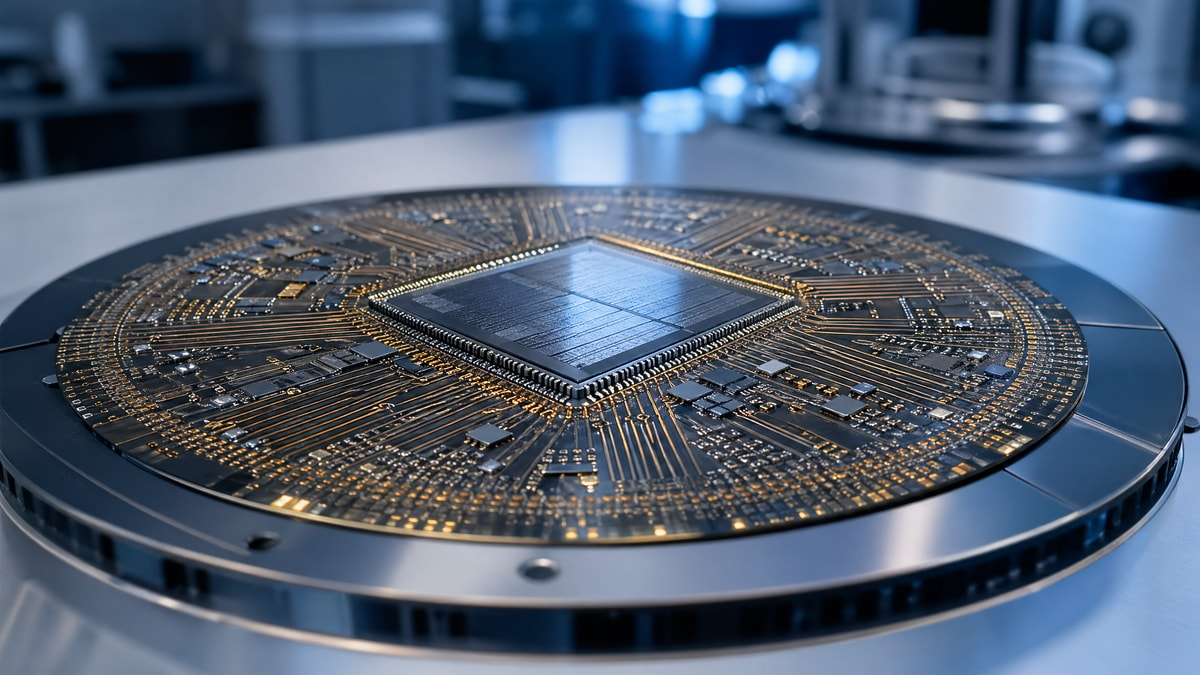

For enterprise leaders expanding semiconductor capacity, a weak Semiconductor Fabrication supplier can trigger costly delays, compliance gaps, and yield instability long before tools go online. As fabs race to secure resilient infrastructure, understanding supplier risks across materials, environment control, packaging, and process support is essential to protecting timelines, capital efficiency, and long-term manufacturing competitiveness.

In practice, capacity expansion is rarely delayed by one visible failure. More often, it slips through a chain of supplier-related issues: a 12-week delay in high-purity gas systems, a missed FAT milestone for cleanroom airflow control, incomplete traceability for wet chemicals, or packaging partners that cannot scale from pilot lots to 30,000 units per month without yield drift.

For CTOs, fab investors, operations leaders, and procurement heads, the challenge is not only finding a Semiconductor Fabrication supplier with technical capability. The real task is identifying which suppliers can support ramp-up under international reliability expectations such as SEMI practices, AEC-Q100-linked quality demands, and ISO/IEC 17025-aligned testing discipline, especially when projects span mature-node fabs, power semiconductor lines, MEMS devices, and advanced packaging ecosystems.

Why Supplier Risk Becomes a Capacity Expansion Risk

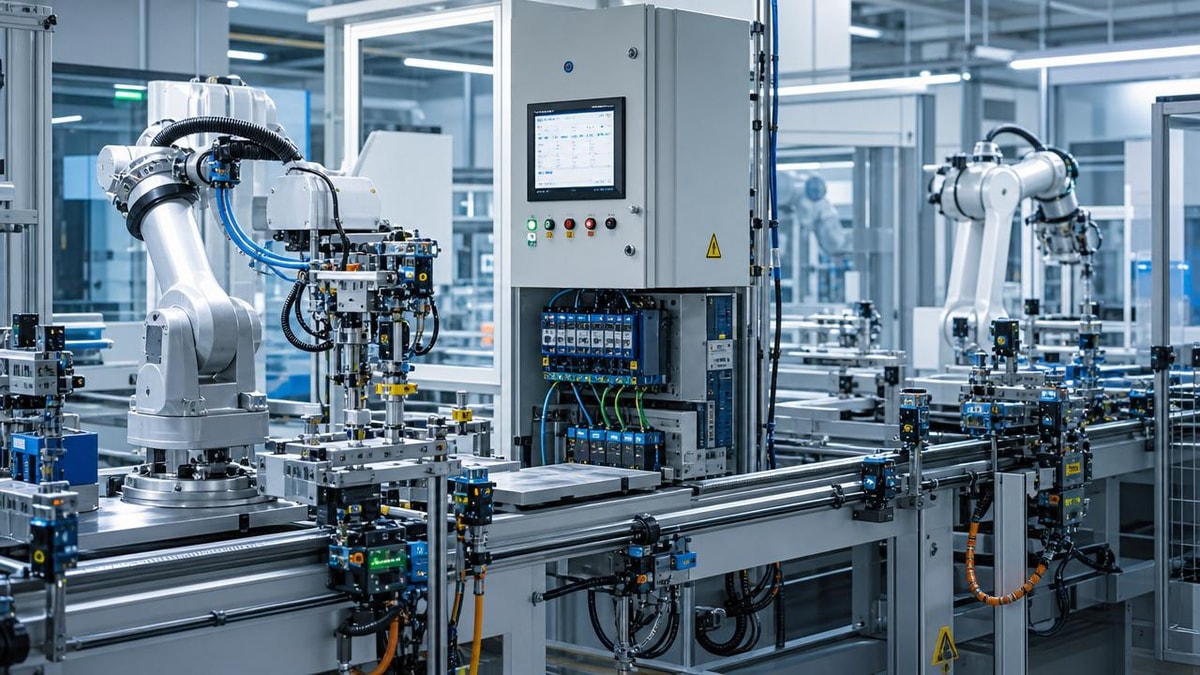

A fab expansion program usually involves 4 to 7 interdependent workstreams: facility build-out, utility systems, tool installation, process qualification, materials onboarding, packaging interface planning, and customer audit readiness. If one Semiconductor Fabrication supplier underperforms, the resulting delay can spread across the entire critical path within 2 to 6 weeks.

This risk is especially acute in 2026 market conditions, where SiC, GaN, industrial MEMS, and automotive-grade electronics require tighter process windows, stronger contamination control, and more disciplined data traceability than standard consumer electronics lines. A supplier that is acceptable for low-mix assembly may be unsuitable for a power device fab where sub-ppb gas purity, thermal uniformity, and chamber uptime directly affect die yield.

The 4 main delay mechanisms

- Late delivery of critical infrastructure such as abatement systems, gas cabinets, ultrapure chemical distribution, or vibration-controlled HVAC modules.

- Specification mismatch between fab design assumptions and the supplier’s actual process capability, often discovered during SAT or early qualification.

- Weak documentation control, including missing calibration records, insufficient material certificates, or poor change-notice discipline.

- Insufficient ramp support after installation, leading to recurring downtime, unstable process repeatability, or slow corrective action cycles.

Where decision-makers often underestimate the problem

Many buyers focus on tool lead time alone, but upstream and adjacent systems matter just as much. A 20-week lithography tool timeline will not protect the schedule if the supporting Semiconductor Fabrication supplier for clean dry air, specialty gas valve manifolds, or AMC control cannot meet the required acceptance window. In some projects, the bottleneck is not equipment availability but supplier readiness to document, integrate, and validate.

The table below highlights common supplier risk categories and how they typically affect fab expansion timing and operating confidence.

The key conclusion is straightforward: the most dangerous Semiconductor Fabrication supplier is not always the most expensive or least known. It is the supplier whose hidden capability gap appears after design freeze, when schedule recovery becomes costly and politically difficult inside a major capital program.

High-Risk Supplier Segments in the Semiconductor Value Chain

Not all supplier categories carry the same risk profile. Enterprise buyers should prioritize those segments where process sensitivity, compliance burden, and installation dependency are highest. In semiconductor expansion, 5 segments deserve deeper scrutiny before purchase orders are fully committed.

1. High-purity electronic chemicals and specialty gases

For wet benches, etch, deposition, and cleaning steps, the Semiconductor Fabrication supplier must demonstrate purity consistency, packaging integrity, and batch traceability. In advanced or power-oriented production, even minor ionic contamination or moisture variation can affect defect density, oxide performance, or long-term reliability. Buyers should expect documented incoming control, retention samples, and change notification periods of at least 60 to 90 days for formulation or source adjustments.

2. Fab environment control and airborne contamination management

Temperature drift of 1°C, humidity instability, or airborne molecular contamination outside the target envelope can undermine lithography alignment, bonding quality, and metrology consistency. A capable Semiconductor Fabrication supplier in this area should define control ranges, sensor placement logic, maintenance intervals, and escalation response times in writing. For many fabs, acceptable drift windows are tighter than general industrial HVAC standards, particularly in packaging, MEMS calibration, and specialty device assembly zones.

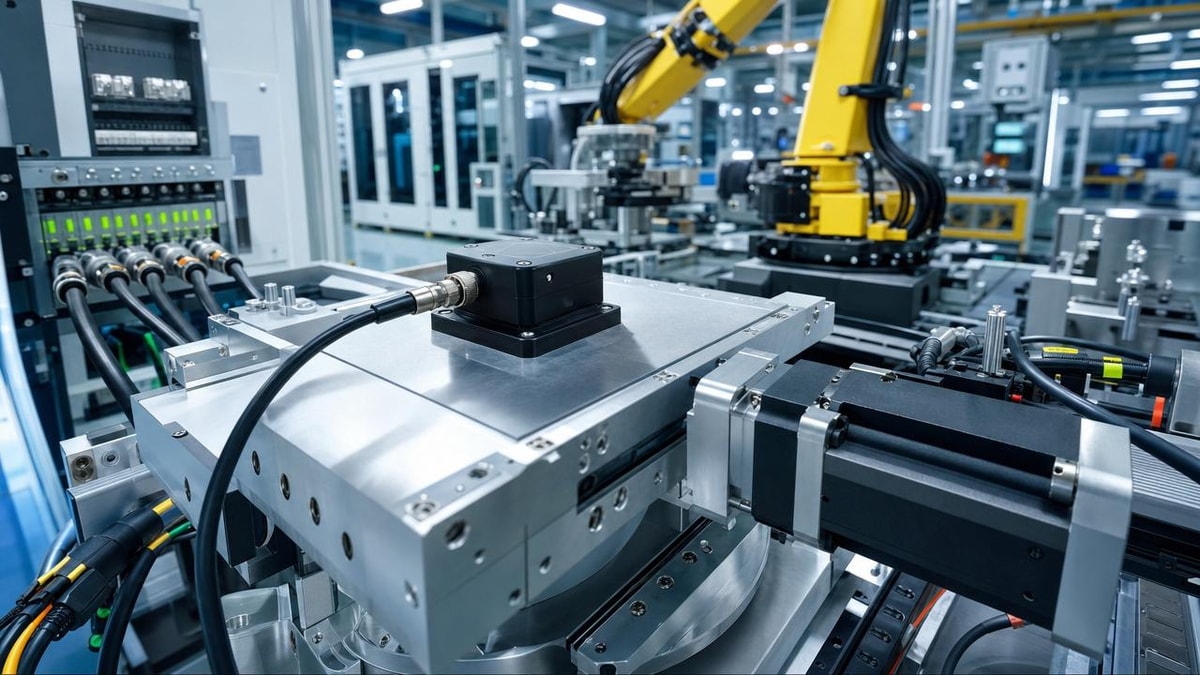

3. Advanced packaging and test support partners

When fab expansion includes 2.5D, 3D integration, wafer-level packaging, or chiplet programs, back-end partners become part of the capacity equation. A weak supplier may pass prototype builds but fail at sustained volume. Decision-makers should verify warpage control capability, substrate sourcing resilience, assembly yield at pilot and mass-production levels, and burn-in or reliability screening alignment. A 3% to 5% drop in package yield can erase much of the value expected from front-end capacity expansion.

4. Power semiconductor and third-generation material ecosystem

SiC and GaN-related expansion carries extra supplier risk due to substrate variation, thermal management sensitivity, and process maturity differences across regions. If the Semiconductor Fabrication supplier cannot support repeatable material specifications, failure analysis turnaround, and lot-to-lot data consistency, line qualification may stretch from 8 weeks to 16 weeks or more.

5. MEMS and sensor-related process support

Industrial-grade MEMS and smart sensors depend on dimensional consistency, packaging protection, and calibrated signal integrity. Here, supplier risk is often linked to process drift that remains hidden until final test, environmental cycling, or field simulation. Enterprises targeting autonomous systems or industrial IoT platforms should treat sensor-line suppliers as strategic, not transactional.

How to Evaluate a Semiconductor Fabrication Supplier Before Delays Occur

A practical evaluation model should move beyond price, lead time, and brochure claims. For most enterprise procurement teams, a 6-point screening framework is more effective because it tests real delivery resilience under fab conditions.

Six checkpoints for supplier selection

- Process capability: Can the supplier meet target purity, tolerance, thermal, vibration, or contamination requirements consistently?

- Documentation depth: Are certificates, calibration logs, test methods, and revision histories complete and current?

- Scale readiness: Can output grow from pilot stage to full ramp within 3, 6, or 12 months?

- Quality response: Is there a defined NCR, CAPA, and engineering escalation process with target closure times?

- Supply continuity: Are dual-source components, buffer inventory, and logistics contingencies in place?

- On-site support: Can the supplier provide installation, qualification, and troubleshooting support within 24 to 72 hours when needed?

What to ask during technical and commercial review

Procurement and engineering should jointly review the Semiconductor Fabrication supplier using scenario-based questions. Ask what happens if a lot fails incoming inspection, if a utility interface changes 30 days before SAT, or if a parameter excursion appears during the first 500 wafers. Strong suppliers answer with process flow, ownership, and recovery timing. Weak suppliers answer with general promises.

The table below can be used as a decision matrix during supplier qualification or quarterly review.

A structured matrix prevents enterprise teams from overvaluing initial price. In large fab programs, a supplier with a 5% higher quote may still be the lower-cost option if it reduces qualification rework, protects uptime, and shortens time to revenue by even 2 to 4 weeks.

Risk Mitigation Tactics That Protect Schedule and Yield

Once a Semiconductor Fabrication supplier is selected, risk management must continue through implementation. The most effective fab operators use milestone-based controls rather than waiting for final acceptance to reveal gaps.

Build a 3-stage control model

Stage 1: Pre-award verification

Review drawings, process assumptions, contamination thresholds, maintenance concepts, and service coverage. For critical systems, include at least 1 on-site audit or remote process review before contract signature.

Stage 2: FAT and interface readiness

Confirm performance against agreed parameters before shipment. This may include flow stability, leak integrity, control logic verification, material compatibility, and documentation completeness. For complex utility packages, enterprises often save 2 to 3 weeks by resolving interface conflicts at FAT rather than after installation.

Stage 3: Ramp and early production control

Track the first 30, 60, and 90 days with defined KPIs: uptime, defect excursions, lot holds, response time, and closure rate for corrective actions. This is where many Semiconductor Fabrication supplier weaknesses become measurable. A formal review rhythm helps prevent small deviations from becoming chronic production losses.

Common mistakes during expansion

- Using generic industrial specifications instead of semiconductor-specific tolerances.

- Approving first articles without complete traceability or retention criteria.

- Assuming back-end packaging partners can absorb volume without separate yield validation.

- Failing to align facility, process, quality, and procurement teams on one acceptance checklist.

- Relying on a single-source supplier for critical materials with no contingency stock or alternate route.

Why Benchmarking Matters for Global Expansion Decisions

For multiregional companies, supplier evaluation cannot depend only on local familiarity. A Semiconductor Fabrication supplier should be assessed against the technical expectations of the end market, whether that means industrial automation, EV power modules, smart sensing platforms, or sovereign digital infrastructure. This is where disciplined benchmarking across materials, packaging, sensing, and fab environment control becomes commercially important.

G-SSI’s institutional focus reflects this reality. As semiconductor programs increasingly connect China’s mature-node manufacturing expansion with global requirements for reliability, thermal control, and data fidelity, enterprise teams need a sharper way to compare supplier capability. The most resilient expansion strategies are built on measurable readiness, not assumptions about geography, scale, or vendor reputation.

If your organization is evaluating a Semiconductor Fabrication supplier for capacity growth, the priority is clear: validate critical risks early, qualify across the full silicon value chain, and align supplier performance with the standards your customers and regulators will actually audit. To reduce delay exposure and build a stronger semiconductor supply base, contact us to discuss your project requirements, request a customized evaluation framework, or explore more solutions for resilient fab expansion.

- Smart Sensors

- Electronic Chemicals

- Semiconductor Fabrication

- Thermal Management

- Data Fidelity

- Industrial IoT

- Autonomous Systems

- Silicon Value Chain

- High-Purity Chemicals

- Environment Control

- Sovereign Digital Infrastructure

- Digital Infrastructure

- Industrial IoT platform

- Semiconductor Fabrication supplier

- Industrial MEMS

- Specialty Gases

Get weekly intelligence in your inbox.

No noise. No sponsored content. Pure intelligence.