Semiconductor Standards Explained for New Capacity Planning

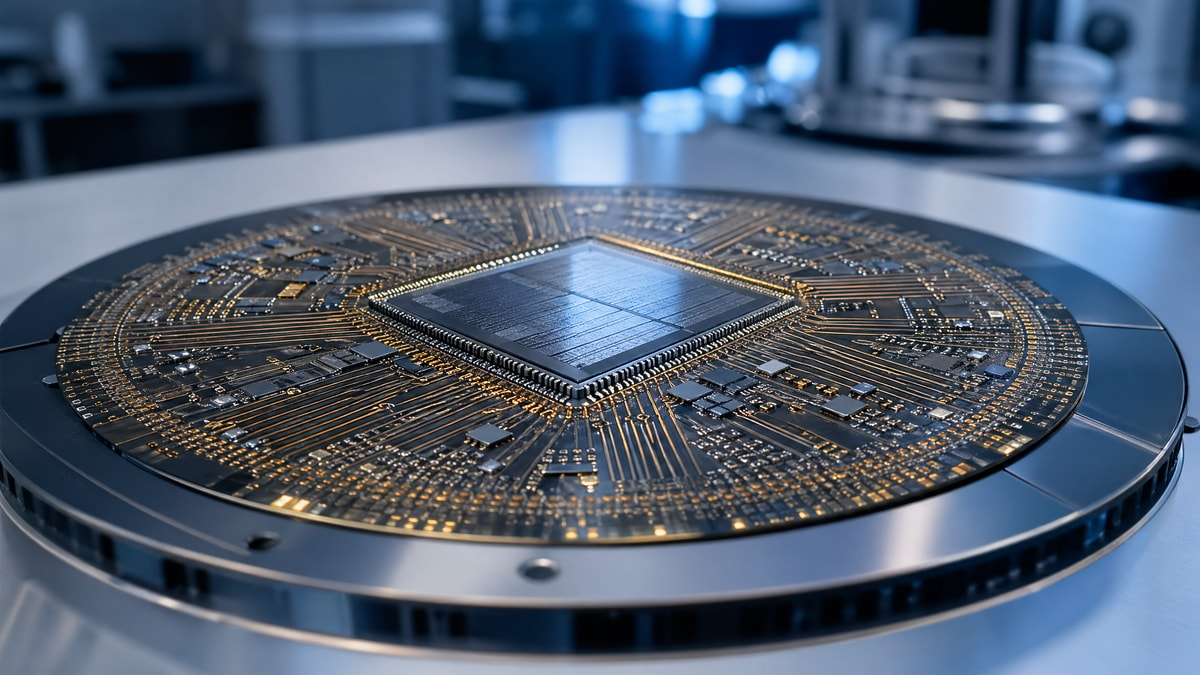

Semiconductor Standards are the foundation of reliable capacity planning, especially when new fabs, packaging lines, or sensor production must scale without compromising quality, yield, or compliance. For project managers and engineering leaders, understanding how standards such as SEMI, AEC-Q100, and ISO/IEC 17025 shape equipment selection, process control, and risk management is essential to building resilient, future-ready operations.

Why Semiconductor Standards Are Becoming a Board-Level Capacity Planning Issue

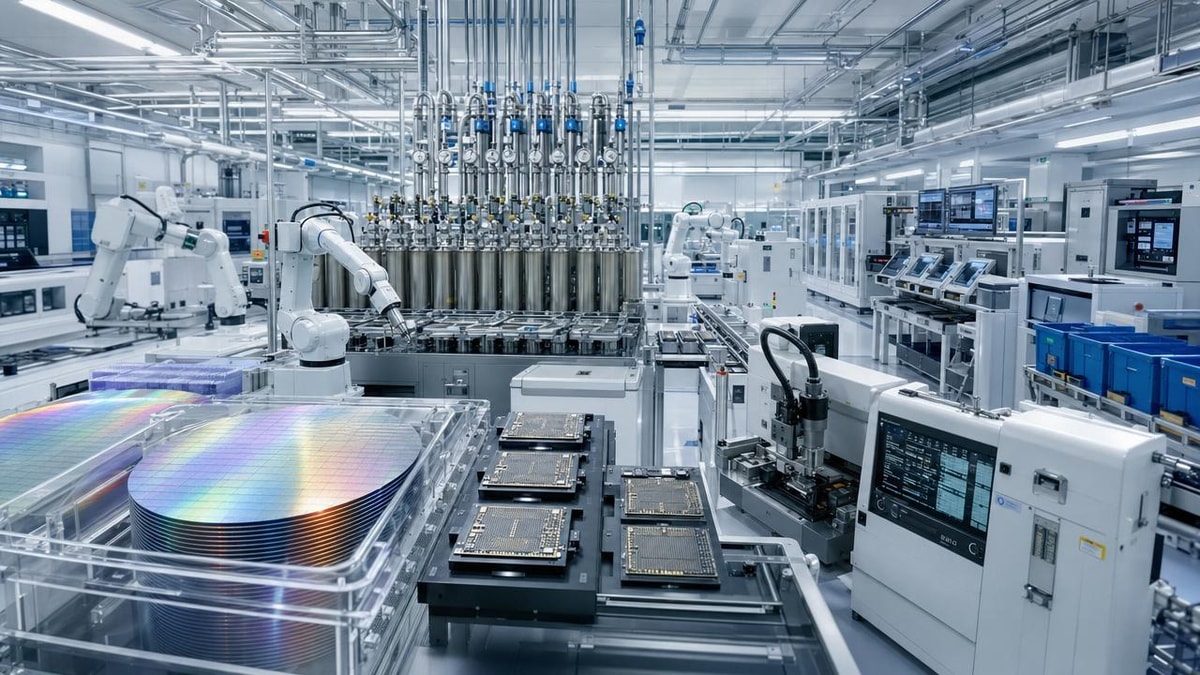

The current shift in semiconductor manufacturing is not only about adding more tools, more cleanroom space, or more output per month. It is about whether new capacity can come online fast enough while still meeting increasingly strict expectations for reliability, traceability, and process stability. In 2026 planning cycles, project managers are being asked to deliver capacity in shorter windows, often within 9 to 18 months, while also supporting more diverse device portfolios such as power semiconductors, advanced packaging, and industrial-grade sensors.

That change has made Semiconductor Standards more important than they were in earlier expansion waves. In the past, some facilities could focus primarily on throughput and later tune quality systems after production ramp. Today, that approach creates major exposure. A fab or backend line that is not aligned early with SEMI safety interfaces, AEC reliability expectations, or ISO/IEC 17025 laboratory discipline may face delayed qualification, unstable yields, repeated customer audits, and avoidable capex rework.

For organizations operating across the silicon value chain, from SiC and GaN devices to MEMS and sensor modules, the standards landscape also affects commercial timing. A delay of even 8 to 12 weeks in tool acceptance, environmental validation, or reliability screening can disrupt launch commitments for automotive, industrial IoT, and energy infrastructure projects. This is why capacity planning has become inseparable from standards planning.

What changed in recent expansion cycles

Several industry signals explain why Semiconductor Standards now influence capacity decisions much earlier. First, product mix has become more complex. Mature-node logic, power discretes, MEMS, chiplet packaging, and sensor-integrated modules often coexist in the same investment roadmap. Second, customer qualification requirements have become more layered, especially when products serve automotive, industrial control, smart energy, or sovereign digital infrastructure. Third, utilities and contamination control now matter more because process windows are tighter and material purity expectations can reach sub-ppb levels for specialty gases.

The result is a planning environment where standards are no longer a late-stage compliance checklist. They act as a design input. Project teams that treat standards as an engineering constraint from day 1 generally reduce redesign loops, improve commissioning readiness, and gain a clearer view of total ramp risk across facility, process, quality, and supply chain functions.

The following table summarizes how capacity planning expectations are shifting and why Semiconductor Standards are now central to project execution.

For project leaders, the main implication is practical: standards alignment should be built into front-end engineering decisions, not added after equipment arrives on site. That single shift can materially improve schedule confidence and launch quality.

The Main Forces Driving Standards-Led Capacity Expansion

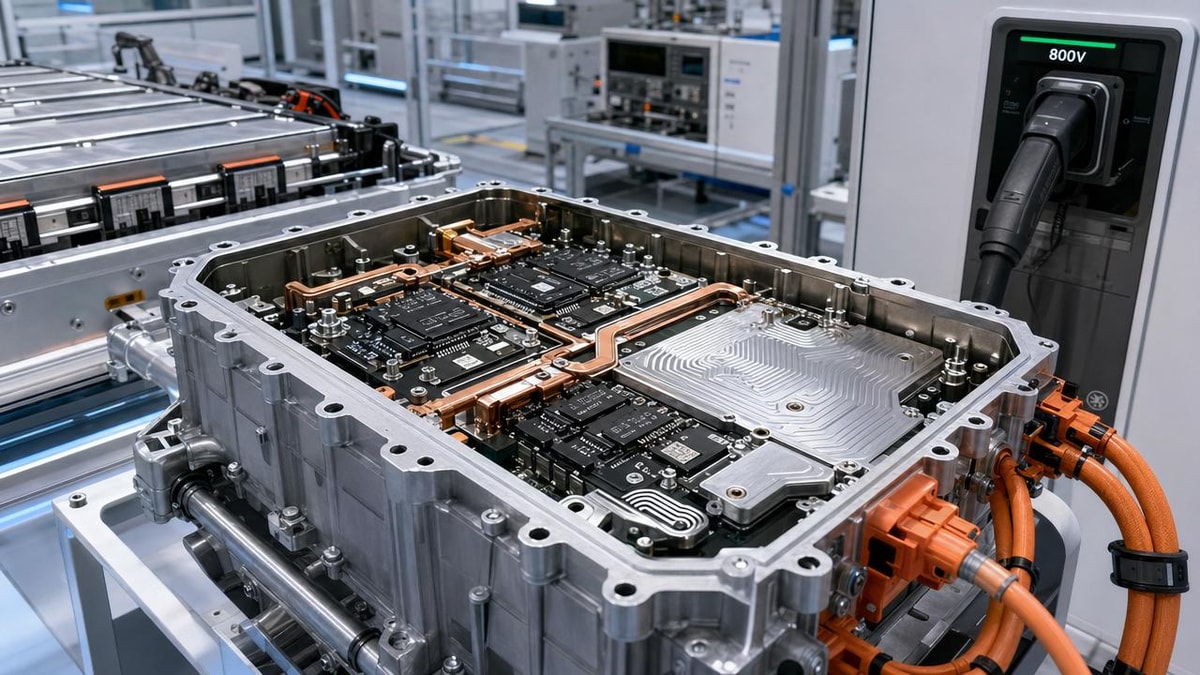

The strongest driver is application criticality. Semiconductor output is increasingly serving electric vehicles, fast-charging systems, industrial automation, smart grids, machine vision, and edge AI sensing. In these environments, failures are more expensive and field conditions are harsher. A power module operating at 650V to 1200V or a sensor deployed in high-vibration industrial equipment cannot rely on informal qualification logic. Standards-based planning becomes part of product risk control.

A second force is the wider use of heterogeneous manufacturing flows. Advanced packaging, wafer-level testing, MEMS assembly, and reliability labs must exchange data cleanly across multiple nodes. That is one reason standards such as SEMI are important beyond equipment safety alone. They influence communication, tool integration, contamination management, and facility interoperability. For a new line, missing one interface requirement can create downstream delays in MES integration, preventive maintenance planning, or traceability validation.

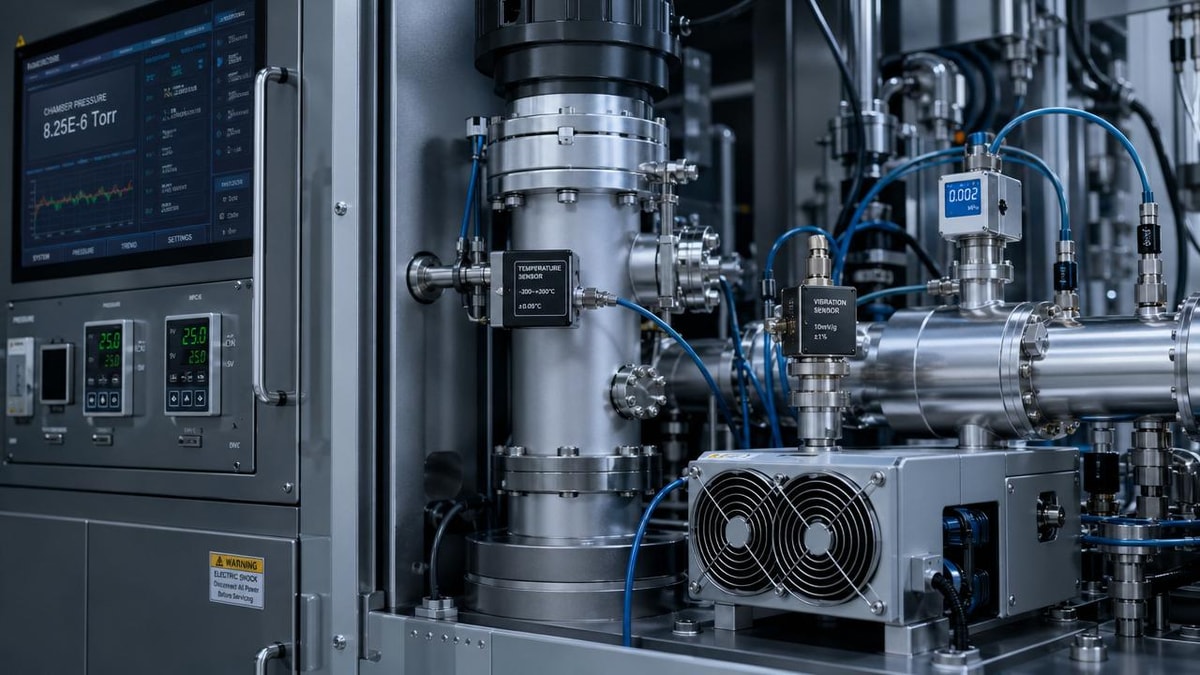

The third force is global customer scrutiny. Even when production targets regional or domestic programs, buyers increasingly expect evidence of disciplined calibration, repeatable testing, and controlled environments. ISO/IEC 17025 matters here because test credibility affects release decisions, failure analysis, and customer confidence. A lab that cannot demonstrate measurement integrity within defined uncertainty ranges may slow qualification for 3 to 6 months.

How key standards influence investment logic

Not all Semiconductor Standards shape projects in the same way. Some affect facility layout, some affect incoming tool specifications, and others affect product qualification or laboratory management. Project managers need a functional map, not only a standards list, because the budget impact and schedule impact occur at different stages.

- SEMI-related requirements often influence tool interfaces, safety integration, utility compatibility, contamination control, and automation readiness.

- AEC-Q100 and related automotive-grade reliability expectations influence stress testing, burn-in planning, failure screening, and release criteria for ICs and modules.

- ISO/IEC 17025 affects calibration systems, test method validation, measurement traceability, and the credibility of lab-generated data used in qualification and customer audits.

- Environmental and purity control practices affect specialty gases, wet chemicals, airborne molecular contamination, and process drift in both fabs and sensor production areas.

When these requirements are mapped early, teams are better able to distinguish which capex items are mandatory for qualification, which are optional for future flexibility, and which should be phased in after pilot production. This prevents overbuilding in some areas while under-specifying critical quality infrastructure in others.

Typical planning windows affected by standards

In many projects, standards decisions affect at least four timing windows: concept design in the first 4 to 8 weeks, equipment specification and procurement over 3 to 6 months, installation and qualification over 2 to 4 months, and controlled ramp over another 8 to 16 weeks. If standards interpretation is delayed until the third window, change orders become more likely and recovery costs rise quickly.

Where Project Managers Feel the Impact First

The direct effect of Semiconductor Standards usually appears in three places: scope definition, vendor coordination, and risk ownership. In scope definition, standards determine what the line must prove before handover. In vendor coordination, they shape what tool makers, utility suppliers, metrology providers, and testing partners must deliver. In risk ownership, they clarify who is accountable when qualification data, contamination performance, or equipment interfaces do not meet expected thresholds.

For engineering project leaders, this matters because schedule pressure often hides standards gaps until late in the build. A line may appear mechanically complete, yet still fail readiness because gas purity verification is incomplete, calibration intervals are undefined, or burn-in capacity does not match the planned qualification sample size. Those issues do not always look large in capex spreadsheets, but they can stop launch decisions.

The impact is especially visible in mixed portfolios. A facility supporting both industrial sensors and power devices may require different screening intensity, environmental control priorities, and validation methods. Standards-driven segmentation of workflows often becomes necessary to avoid applying a single qualification logic to fundamentally different products.

Impact by business function

The table below shows how Semiconductor Standards influence different participants in a new capacity program.

This impact pattern shows why standards ownership cannot sit only inside quality teams. In practice, Semiconductor Standards influence engineering design, procurement timing, commissioning logic, and long-term maintainability.

Common pressure points during ramp

- Tool acceptance criteria that do not fully reflect required interface, safety, or contamination conditions.

- Reliability screening capacity that is too small for pilot lots, especially when sample plans expand after customer review.

- Laboratory setups that have instruments installed but do not yet have validated methods, traceable calibration, or defined uncertainty budgets.

- Facility systems that meet general cleanroom targets but not the specific chemical, gas, or AMC control needed for sensitive processes.

Each of these issues can add 2 to 10 weeks depending on whether the line supports mature-node wafers, advanced packaging, or industrial sensor manufacturing. The earlier they are surfaced, the lower the ramp disruption.

What to Watch When Planning New Fabs, Packaging Lines, and Sensor Capacity

The most effective response is not to chase every standard in equal depth. Instead, project teams should identify which Semiconductor Standards materially affect launch success for their product mix, customer base, and intended qualification route. A 200 mm mature-node power line, a 2.5D packaging line, and a MEMS sensor assembly line each require a different emphasis, even if they share some core infrastructure principles.

For power semiconductors, thermal cycling, high-voltage handling, material robustness, and package reliability are often central. For advanced packaging, alignment precision, underfill control, substrate interaction, and test traceability may dominate. For industrial sensors, calibration stability, environmental drift, and data fidelity under field stress can become more important than raw wafer throughput. Standards should therefore be translated into line-specific readiness criteria.

Project teams also need to separate mandatory launch conditions from future-scale options. For example, a line may need full calibration discipline and critical contamination control before pilot release, but it may phase some advanced automation or expanded lab redundancy into the next 6 to 12 months. That distinction improves capital efficiency while keeping qualification risk visible.

A practical screening framework

Before freezing the investment package, many organizations benefit from using a structured review covering at least the following points.

- Product-risk mapping: define whether the line supports consumer, industrial, automotive-adjacent, or critical infrastructure applications.

- Standards mapping: identify which Semiconductor Standards apply to tools, labs, utilities, packaging flows, and release testing.

- Supplier readiness review: confirm lead times, documentation depth, FAT support, spare strategy, and interface compatibility.

- Ramp bottleneck analysis: estimate whether pilot lots, reliability chambers, metrology steps, or contamination verification will constrain output in the first 90 days.

- Audit-readiness planning: decide what evidence must exist before customer visits or internal release boards.

Suggested priority matrix for new capacity projects

The table below offers a practical way to prioritize standards-related workstreams during capacity buildout.

This matrix helps engineering leaders avoid a common error: overemphasizing visible mechanical progress while underfunding the invisible systems that enable qualification credibility and repeatable output.

How to Turn Standards into a More Resilient Expansion Strategy

The strategic value of Semiconductor Standards is not only compliance. It is resilience. A standards-led capacity plan can improve supplier substitution readiness, reduce audit friction, and support smoother migration from pilot runs to stable production. For organizations balancing local supply development with international acceptance criteria, this is especially important. The more clearly standards are translated into engineering specifications, the easier it becomes to benchmark domestic and international options on equal technical terms.

A resilient strategy usually starts with a benchmark framework covering five pillars: process compatibility, facility environment, test credibility, reliability readiness, and supply chain continuity. These pillars align closely with the needs of modern silicon programs, particularly in SiC/GaN, advanced packaging, industrial MEMS, specialty chemicals, and controlled fab environments. When a capacity project is reviewed through these lenses, hidden dependencies become easier to detect before they affect launch.

For example, an expansion may appear sufficiently funded on paper, yet still be vulnerable if specialty gas purity control is underdefined, if metrology traceability is weak, or if package reliability testing is outsourced without clear turnaround guarantees. In practical terms, a resilient line often depends on whether critical support systems can hold target performance over the first 3 to 6 months of ramp, not only whether they pass initial startup tests.

Recommended decisions for the next planning cycle

- Build a standards matrix before equipment release, linking each requirement to owner, timing, verification method, and launch impact.

- Segment qualification logic by product family instead of applying one generic checklist to all devices and packages.

- Verify that labs, reliability resources, and facility controls can support projected pilot volumes, not just steady-state assumptions.

- Use supplier benchmarking to compare not only price and lead time, but also documentation quality, maintainability, and standards alignment.

- Review whether future customer mix may require tighter reliability or traceability expectations within the next 12 to 24 months.

These actions help project managers move from reactive compliance to forward-looking decision support. That is the real planning value of Semiconductor Standards in a market where technology transitions, application criticality, and customer scrutiny are all rising at the same time.

Why Work With Us on Standards-Led Capacity Planning

G-SSI supports project managers, CTOs, IC design leaders, and industrial IoT architects who need practical interpretation of Semiconductor Standards across the real operating conditions of new capacity programs. Our focus covers power semiconductors and third-generation materials, advanced packaging and testing, industrial-grade MEMS and smart sensors, high-purity electronic chemicals and specialty gases, and semiconductor fabrication environment control.

Instead of treating standards as isolated documents, we help translate them into project decisions: which parameters need early confirmation, which equipment or material options fit your process intent, what delivery windows may affect ramp timing, where certification or lab-readiness questions could create bottlenecks, and how customized benchmarking can support a more confident expansion path.

If you are evaluating new fab capacity, a packaging line upgrade, sensor production expansion, or a supporting environment-control and materials strategy, contact us to discuss your priorities. We can help you review specification parameters, product and supplier selection logic, expected delivery cycles, customized solution options, applicable certification requirements, sample support needs, and quotation planning for the next stage of execution.

- Power Semiconductors

- Smart Sensors

- Electronic Chemicals

- Semiconductor Fabrication

- Data Fidelity

- Industrial IoT

- Semiconductor Standards

- Silicon Value Chain

- Third-Generation Materials

- Environment Control

- Sovereign Digital Infrastructure

- Industrial-Grade Sensors

- 2.5D Packaging

- Digital Infrastructure

- Industrial MEMS

- Specialty Gases

Get weekly intelligence in your inbox.

No noise. No sponsored content. Pure intelligence.