IC Cleaning Solvent Selection Risks in Advanced Packaging

Selecting the wrong IC cleaning solvent in advanced packaging can quietly undermine yield long before failures appear in qualification or field use. In wafer-level packaging, flip-chip assembly, fan-out structures, 2.5D interposers, and heterogeneous integration, residues that seem minor at the cleaning stage can later amplify under heat, bias, moisture, and mechanical stress. That is why Electronic Chemicals for Semiconductor must be evaluated not only for immediate cleaning power, but also for compatibility with underfill interfaces, ultra-fine pitch metallization, low-k materials, mold compounds, and reliability targets. For organizations building resilient semiconductor infrastructure, solvent selection is a process control decision with direct impact on corrosion risk, delamination behavior, ionic cleanliness, and long-term package stability.

Why solvent selection risk changes across advanced packaging scenarios

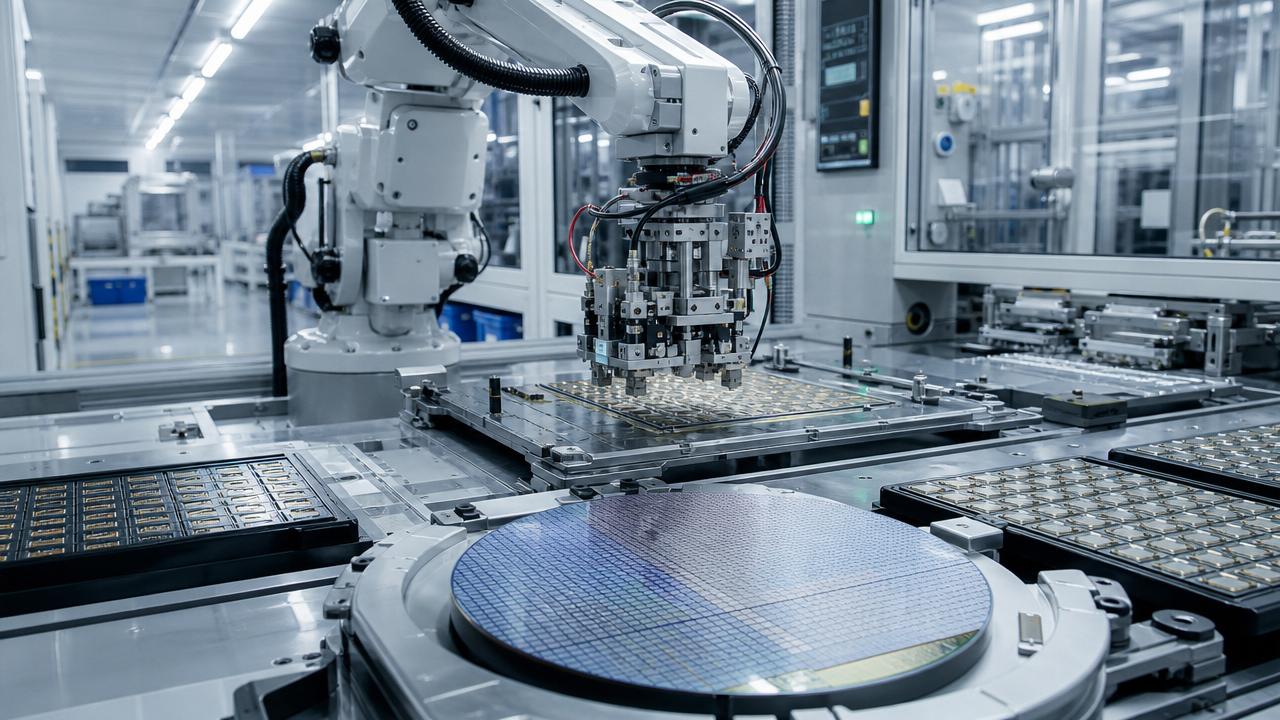

Advanced packaging is not a single cleaning environment. A solvent that performs adequately in conventional wire-bond assembly may become unacceptable in fine-pitch bumping, through-silicon via structures, or chiplet integration. The reason is simple: package architectures now combine dissimilar materials, tighter geometries, lower process windows, and higher thermal density. In these conditions, Electronic Chemicals for Semiconductor are interacting with more surfaces, thinner interfaces, and narrower margins for error.

Risk also shifts depending on the contamination source. Flux residues, polishing remnants, dicing contaminants, mold release traces, adhesive bleed-out, and ionic particles do not respond equally to the same chemistry. Selection must therefore start with a scenario-based question: what exactly needs to be removed, from which material stack, under what drying and reliability constraints? Without that framing, even high-purity Electronic Chemicals for Semiconductor can create avoidable failure modes.

Scenario 1: Fine-pitch flip-chip and micro-bump cleaning where residue becomes latent failure

In fine-pitch flip-chip and micro-bump assembly, cleaning is difficult because capillary spaces trap flux activators and partially dissolved residue. A solvent that removes visible contamination from open surfaces may leave concentrated residue beneath bumps or around solder joints. This creates a hidden reliability threat: electrochemical migration, dendritic growth, and contact degradation during humidity bias testing.

The key judgment point in this scenario is not aggressive solvency alone. It is penetration, residue lift-off behavior, rinseability, and drying completeness. Electronic Chemicals for Semiconductor used here should show low nonvolatile residue, strong compatibility with Cu pillars, SnAg solder, Ni/Au finishes, and no adverse interaction with under-bump metallurgy. If cleaning leaves a thin organic film, underfill adhesion may also decline, increasing the chance of interface cracking during thermal cycling.

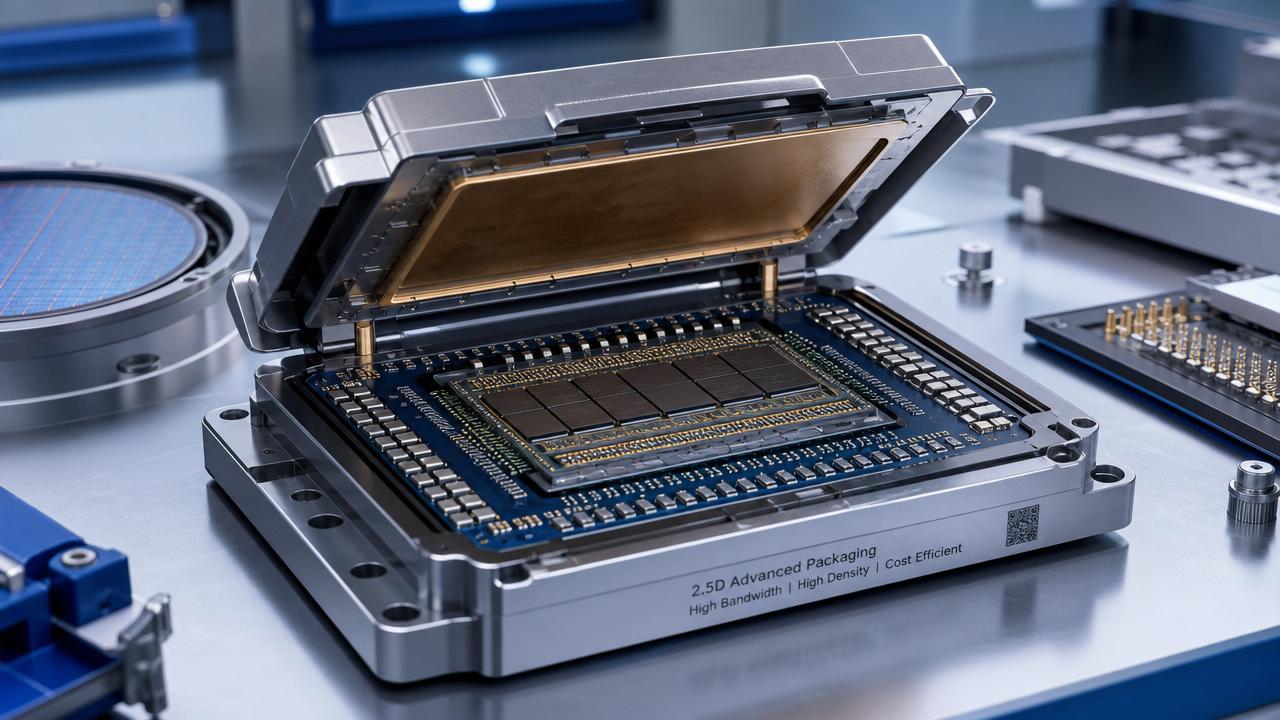

Scenario 2: Fan-out and wafer-level packaging where material compatibility is the primary risk

Fan-out wafer-level packaging and panel-level processing introduce a broader set of polymeric materials, redistribution layers, dielectric films, photo-patternable compounds, and temporary bonding systems. In this environment, the wrong cleaning chemistry can cause swelling, softening, surface haze, dielectric attack, or bond-line weakening. Damage may not be obvious after cleaning, yet later manifests as warpage increase, delamination, or crack initiation.

The selection focus for Electronic Chemicals for Semiconductor in fan-out applications is balanced chemistry. The solvent must remove residue without altering surface energy in a way that compromises subsequent coating, molding, or metallization. Compatibility testing should cover low-k films, polyimide, epoxy mold compounds, dry films, and temporary adhesives. If the package route includes plasma, laser debond, or high-temperature reflow, solvent exposure should also be assessed in the full process sequence rather than as a standalone cleaning step.

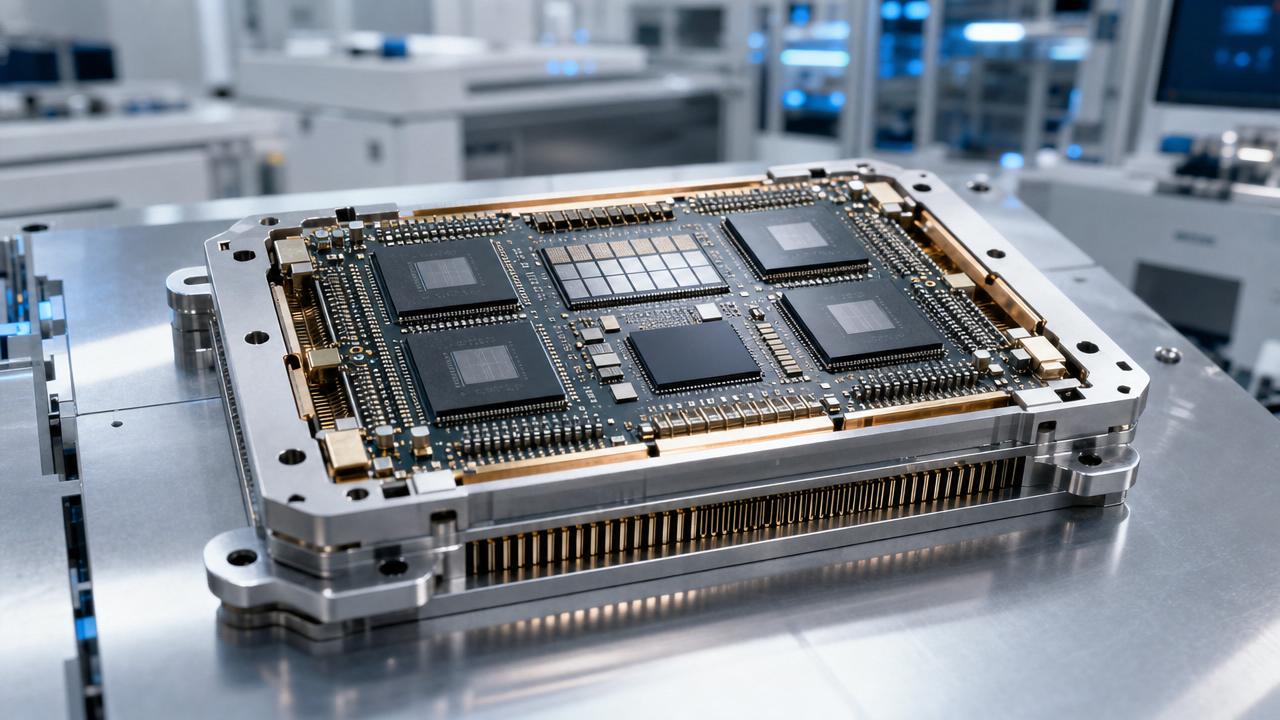

Scenario 3: 2.5D, 3D, and chiplet structures where trapped chemistry drives corrosion risk

In 2.5D interposers, 3D stacking, and chiplet-based integration, package density and interface complexity make cleaning verification more difficult. Cavities, sidewalls, microvias, TSV-related structures, and edge regions can retain solvent or dissolved residue if volatility and drying behavior are not properly matched to the geometry. A chemistry that appears clean in short-term inspection can still leave ionic traces in inaccessible regions.

Here, the main decision point is whether Electronic Chemicals for Semiconductor support complete removal and complete evacuation. Corrosion of copper redistribution features or interposer routing can begin with sub-visible residue, especially when packages operate at elevated temperature with frequent power cycling. For high-value chiplet assemblies, solvent selection should be linked to ion chromatography, surface insulation resistance, and highly accelerated stress results, not just visual cleanliness.

How scenario requirements differ in practice

Practical selection criteria for Electronic Chemicals for Semiconductor

A reliable solvent screen should move beyond generic labels such as “high purity” or “precision cleaning grade.” In advanced packaging, Electronic Chemicals for Semiconductor should be assessed against a structured set of criteria tied to package architecture and downstream reliability expectations.

- Chemical purity and ionic profile, including trace metals, halides, and nonvolatile residue

- Compatibility with Cu, Al, Ni, Au, solder alloys, passivation layers, low-k films, and package polymers

- Cleaning effectiveness against the specific contaminant load rather than broad assumptions about flux type

- Evaporation rate and drying behavior matched to cavity depth, pitch density, and equipment capability

- Rinse process fit, including water compatibility, semi-aqueous behavior, and residue redeposition risk

- Environmental, safety, and compliance fit with site controls and international semiconductor handling standards

This is where benchmarking matters. Within high-performance semiconductor ecosystems, Electronic Chemicals for Semiconductor should be selected with reference to process stability, not procurement convenience. A solvent that slightly improves short-term cleaning speed but increases long-term failure variability is usually the more expensive choice.

Common misjudgments that distort solvent decisions

Several errors appear repeatedly in advanced packaging solvent reviews. The first is assuming visible cleanliness equals ionic cleanliness. Many corrosion-driven failures begin with contamination levels that cannot be detected by optical inspection. The second is evaluating Electronic Chemicals for Semiconductor only on coupon tests or open-surface trials, which do not reproduce real package confinement.

Another common issue is separating chemistry review from package reliability review. In practice, solvent choice influences underfill adhesion, mold compound interaction, dielectric stability, and bias-related leakage. A further mistake is ignoring sequence effects. For example, a solvent may be acceptable before one thermal excursion but harmful after multiple reflow passes or plasma activation. Finally, teams often underestimate how drying conditions, equipment design, and rinse quality alter the real-world performance of Electronic Chemicals for Semiconductor.

Scenario-based recommendations for lower-risk implementation

- For fine-pitch interconnects: prioritize low-residue solvent systems and verify removal in hidden interfaces through SIR and ion analysis.

- For fan-out and WLP: build a material compatibility matrix before pilot release, covering polymers, dielectrics, adhesives, and post-clean adhesion behavior.

- For 2.5D and 3D structures: focus on drying completeness, trapped chemistry risk, and corrosion sensitivity under accelerated environmental stress.

- For mixed-material package flows: qualify Electronic Chemicals for Semiconductor against the entire process route, not isolated cleaning steps.

- For global quality alignment: connect solvent approval to SEMI-referenced cleanliness expectations, reliability data, and traceable lab methods consistent with ISO/IEC 17025 discipline.

Next-step actions for stronger packaging decisions

A sound next step is to classify each advanced packaging flow by contamination type, geometry severity, material sensitivity, and reliability exposure. That framework helps narrow which Electronic Chemicals for Semiconductor are genuinely suitable instead of broadly acceptable on paper. Follow that with controlled trials that measure not only cleaning efficiency, but also residue, corrosion tendency, adhesion retention, and stress-test behavior.

In a market where packaging complexity is rising alongside performance demands, solvent selection should be treated as a strategic enabler of yield and reliability. The best decisions come from aligning chemistry choice with package scenario, standards-based validation, and full-process compatibility. For organizations advancing sovereign-grade semiconductor capability, rigorous evaluation of Electronic Chemicals for Semiconductor is not a minor process detail; it is part of building durable, high-precision, globally benchmarked packaging infrastructure.

Get weekly intelligence in your inbox.

No noise. No sponsored content. Pure intelligence.